## إلى الكمعانية كلية التربية

## Lecture 7

# Microprocessors

Prepared By:

Firas Abdulrahman Yosif

## **Memory Segmentation**

### Memory Segmentation:

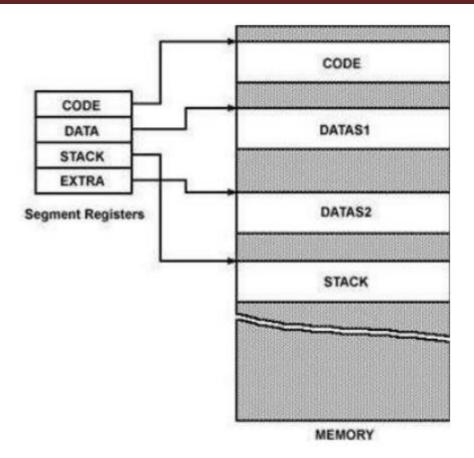

- The memory in an 8086 based system is organized as segmented memory.

- The CPU 8086 is able to access 1MB of physical memory. The complete 1MB of memory can be divided into 16 segments, each of 64KB size and is addressed by one of the segment register.

- The 16-bit contents of the segment register actually point to the starting location of a particular segment. The address of the segments may be assigned as 0000H to F000h respectively.

- To address a specific memory location within a segment, we need an offset address. The offset address values are from 0000H to FFFFH so that the physical addresses range from 00000H to FFFFFH.

- A program can have more than four segments, but can only access four segments at a time.

**Memory Segmentation**

## **Physical Address**:

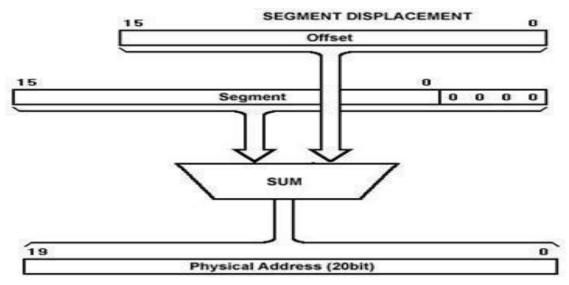

لاحظنا أن الذاكرة بطول 1 ميغا بايت أي أنها مرقمة من 00000h إلى FFFFFh لذلك فإننا نحتاج أثناء عنونة المقاطع إلى رقم ست عشري بطول 20 بت وذلك لأن تمثيل رقم ست عشري بطول خمس خانات(وهو المستخدم في ترقيم حجرات الذاكرة) يحتاج إلى عشرين بت ولكن سجلات المقاطع و التي نستخدمها في العنونة هي بطول 16 بت فقط الأمر الذي يضطرنا إلى استنتاج عنوان فيزيائي بسعة عشرين بت للوصول الى جميع مواقع الذاكرة التي حجمها 1MB.

وعندما تحتاج وحدة مواجهة المسارات Bus Interface Unit الوصول الى الايعازات المعطيات في الذاكرة فأنها تقوم بتوليد العنوان الفيزيائي Physical Address من العنوان المنطقي (Logical address) داخل الـ processor ومن ثم يتم حسابه داخل وحدة التنفيذ execution unit

يتمثل العنوان الفيزيائي بـ 20 bit حيث من خلاله يتم الوصول الى جميع مواقع الذاكرة RAM ويتم حسابه حسب العلاقة التالية:

Physical Address= Segment register x 10 + Offset register

والمخطط في الشكل (1)ادناه يمثل عملية توليد العنوان الفيزيائي:

Figure (1) Block Diagram of Physical Address Generation Operation

The physical Address is obtained in the following way:

- 1) نأخذ قيمة سجل المقطع الممثلة بالنظام الست عشري و نضربها بعشرة في النظام الست عشري فتنزاح قيمة سجل مقطع الذاكرة خانة واحدة نحو اليسار فنحصل على سجل ذات 20 bit .

- 2) نجمع قيمة السجل المساعد او يسمى العنوان الفعال effective address مع مقطع الذاكرة و الممثلة أيضاً بالنظام الست عشري فتكون النتيجة هي حصولنا على العنوان الفيزيائي

Physical Address=مقطع الذاكرة x( 10h ) + (effective address)

#### **Offset Register:**

يتمثل العنوان الازاحة بـ 16 bit ويشمل جميع السجلات التي تتحرك داخل مقاطع الذاكرة مثل Lower offset address وهناك عنوان ازاحة ادنى DI, SI, SP, BP, BX, IP السجلات FFFF وعنوان ازاحة الاعلى Higher offset address والذي يقابل 0000 وعنوان ازاحة الاعلى الموجود داخل مقاطع الذاكرة.

ملاحظة مهمة: السجل CS يتعامل دائما مع السجل IP ومقطع الذاكرة DS يتعامل دائما مع السجل SS و DI و DI و SI و المؤشر SI و DI و اخيرا المقطع SS يتعامل فقط مع السجل BP و SP و SP .

#### **Logical Address:**

العنوان المنطقي والذي يربط مؤشر الازاحة مع مقطع الذاكرة ويتمثل بالعلاقة التالية:

Segment of memory: Offset register

Ex1) Assume CS=024F6h, IP=0634Ah, perform:

- Physical address

- Logical address

- Offset address

- Lower offset address

- Higher offset address

#### Sol.)

1. Physical Address= segment register X 10+offset register

Physical Address= CSX 10 + IP

#### $= 024F6h \times 10 + 0634Ah = 2B2AA$

2. Logical address = Segment of memory: Offset register

Logical address = 024F6h : 0634Ah

- 3. Offset address = 0634Ah

- 4. Lower offset address = 024F6h x10+0000 = 024f60h

- 5.Higher offset address = 024F6h x10 + FFFF =034F5Fh

**Ex2**) Assume BP=024D7h, IP=0B344h and SS = 058A6h perform:

- Physical address

- Logical address

- Lower offset address

- Higher offset address

## Sol.)

1. Physical Address= segment register X 10+offset register

Physical Address= SSX 10 + BP

$= 058A6h \times 10 + 024D7h$

= 05AF37H

2. Logical address = Segment of memory: Offset register

Logical address = 058A6h : 024D7h

3. Lower offset address =  $058A6h \times 10+0000$

= 058A60H

4. Higher offset address = 058A6h x10 + FFFF = 068A5FH

**Ex3**) Assume BP=03A87h, SI=09F44h and DS=0C842h perform:

- Physical address

- Logical address

- Lower offset address

- Higher offset address

#### Sol.)

1. Physical Address= segment register X 10+offset register

Physical Address= DS X 10 + SI

$= 0C842h \times 10 + 09F44h$

= 0D2364H

2. Logical address = Segment of memory: Offset register

Logical address = 0C842h : 09F44h

3. Lower offset address =  $0C842h \times 10+0000$

= 0C8420H

4. Higher offset address =  $0C842h \times 10 + FFFF = 0D841FH$

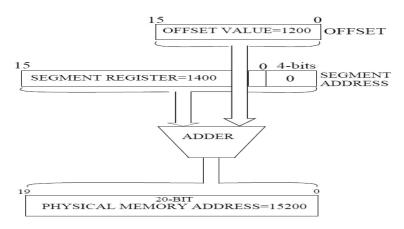

تحدد هذه المجموعة (CS: IP) التعليمات التالية التي يتم تنفيذها بواسطة المعالج الدقيق . يوضح الشكل (2) مثالًا على أنه إذا كان CS = 1400H و CS = 1200H ، فإن المعالج الدقيق يجلب التعليمات التالية من موقع الذاكرة:

Physical address=Segment base address\*10+Offset(Effective)

$$P.A = CS \times 10 + EA$$

=1400H\*10+1200H=15200H

Figure (2) generating a physical address

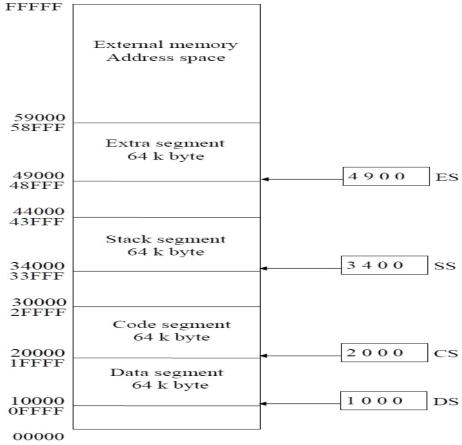

يحدد سجل مقطع الكود بداية مقطع الرمز ويحدد مؤشر التعليمات موقع التعليمات التالية داخل مقطع الرمز والشكل (3) يوضح عناوين بدايات ونهايات مقاطع الذاكرة مع السجلات التي تتعامل معها.

Figure (3) A memory system showing the placement of four memory segments.

The main advantages of the segmented memory scheme are as follows:

- 1. يسمح بسعة اكبر للذاكرة لتكون 1 ميغا بايت على الرغم من أن العناوين الفعلية التي سيتم التعامل معها بحجم 16 بت.

- 2. يسمح بوضع الكود والبيانات وأجزاء المكدسة من نفس البرنامج في أجزاء مختلفة من الذاكرة ، وذلك لحماية البيانات والرموز.

- 3. يساعد على سهولة التعامل مع خزن البيانات في مواقع الذاكرة وبالتالي سرعة القراءة والكتابة من قبل المعالج.